Table of Contents

Dante™ information

DHD devices with Dante interface

DSP Cores

The following DSP Cores have a built-in 4ch/4ch Dante interface.

- 52-7420 (52/XC2)

- 52-7423 (52/XC2)

- 52-7410 (52/XC2)

- 52-1810 (52/XS2)

- 52-1830 (52/XS2)

- 52-7500 (XS3 IP core)

The Dante signal is available on the ETH port on the rear of the DSP core. Only the 52-7500 XS3 core has a separate ethernet interface for the Dante 4×4.

All XC2, XS2, XC3, XD3, XS3 cores and the 52-7310A and 52-7510A Concentrator have an additional expansion slot. You can insert there a Dante IP audio interface.

I/O interfaces

- 52-7080A - XC2 Dante IP Audio Interface

- internal module for 52/XC2, 52/XS2 cores and 52/XC2 Concentrators

- 64 ch in and 64 ch out

- 52-7180A - XC Dante IP Audio Interface

- external module with APC connector for 52/XC, 52/XD, 52/XS, 52/XC2, 52/XD2 and 52/XS2 cores

- 48 ch in and 48 ch out

- 52-7580A - IPx Dante Audio 64×64

- internal module for XC3, XS3, XD3 cores and XC3 Concentrators

- 64 ch in and 64 ch out

- 52-7585A - IPx Dante Audio 512×512

- internal module for XC3, XS3, XD3 cores and XC3 Concentrators

- 512 ch in and 512 ch out

Default network settings at delivery

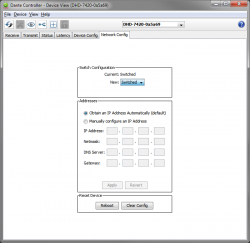

The following table shows the factory settings for the Dante interfaces in DHD devices. You can change the parameters in Dante Controller - Device View - Network Config tab.

| interface type | module | IP Address setting | Switch Configuration |

|---|---|---|---|

| built in 4ch/4ch Dante interface | 52-7420A, 52-7423A, 52-7410A, 52-1810A, 52-1830A | Obtain an IP Address Automatically | not available |

| built in 64ch/64ch Dante interface | 52-7080A | Obtain an IP Address Automatically | redundant |

| 48ch/48ch Dante interface | 52-7180A | Obtain an IP Address Automatically | redundant |

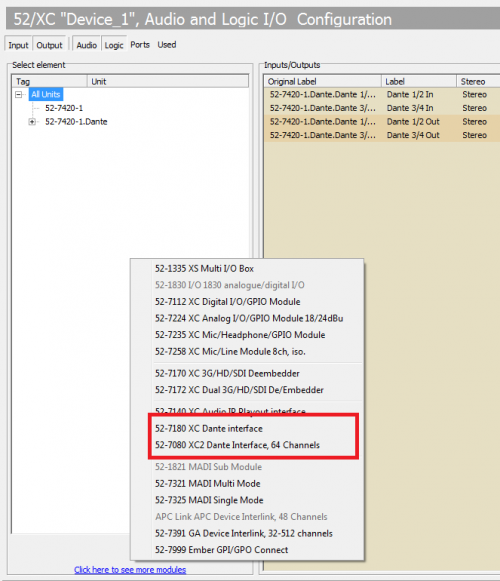

Adding a Dante device in Toolbox

You can add a Dante device in TB via I/O Overview menu. Click Add and select your type of Dante device. If your core device is equipped with a Dante 4×4 interface, the I/Os of it are added automatically when you add your core device. It is named “<Core Name>.Dante” by default.

For more information on adding and using I/O units, see Toolbox9 Documentation - I/O Overview.

Network Switches

General recommendations:

- Use managed switches

- Turn off EEE (Green Ethernet)

Tested network switches

- Cisco Small Business SG300-10

- Cisco Small Business SG300-20

AES67

supported devices

- 52-7080

- 52-7180

- 52-7580

- 52-7585

- 4×4 ch Dante interface in 52-7500 XS3 cores

Note

The AES67 option for supported DHD Dante Modules is available since Dante software version 3.9.6.1.

Updates for DHD's Dante modules are directly provided by DHD.

Important

The 4ch/4ch Dante interface in 52/XC2 and 52/XS2 cores does not support AES67.

PTP in Dante devices and AES67-enabled Dante devices

Dante uses the Precision_Time_Protocol (PTP) in version 1 (IEEE 1588-2002).

Dante supports PTP version 2 (IEEE 1588-2008), when the AES67 mode is enabled.

If you enable the AES67 support on a Dante device, it enables both IEEE PTP v1 and v2. A single clock domain exists across both PTP v1 and v2 devices:

- Standard Dante devices supporting PTP v1 only.

- AES67-enabled Dante devices supporting PTP v1 and PTP v2.

- 3rd-party AES67 devices supporting only PTP v2.

One AES67-enabled Dante device will act as a boundary clock between PTP v1 and v2, bridging the two clock domains. Additional clocking status information is available in Dante Controller for PTP v2 clocking.

Mandatory update for 52-7080A XC2 Dante Interface

Audinate has released version 4.2.0.28 of their Dante firmware. We have carefully tested and released this firmware for our 52-7080A modules.

Important

This update is mandatory. Please do install the update to all existing 52-7080A modules - with or even without issues.

This update is mandatory. Please do install the update to all existing 52-7080A modules - with or even without issues.

The update is available at our Support Portal and can be applied using the Dante Updater.

The update addresses an issue that causes network packets not being correctly received by the Dante module. This issue could lead to single crackles or even more distorted audio signals in streams received by the module. Also synchronisation of the module to the PTP audio clock might be affected.

In the case that your customers report such an issue, the module must be updated first to ensure the above mentioned Audinate firmware issue is excluded. Sending in the module for repair is only required if the 52-7080A module is not responding at all.

52-7080B modules or 52-7180A modules or modules for the XC3 cores (52-7580A / 52-7585A) are not affected by this issue.